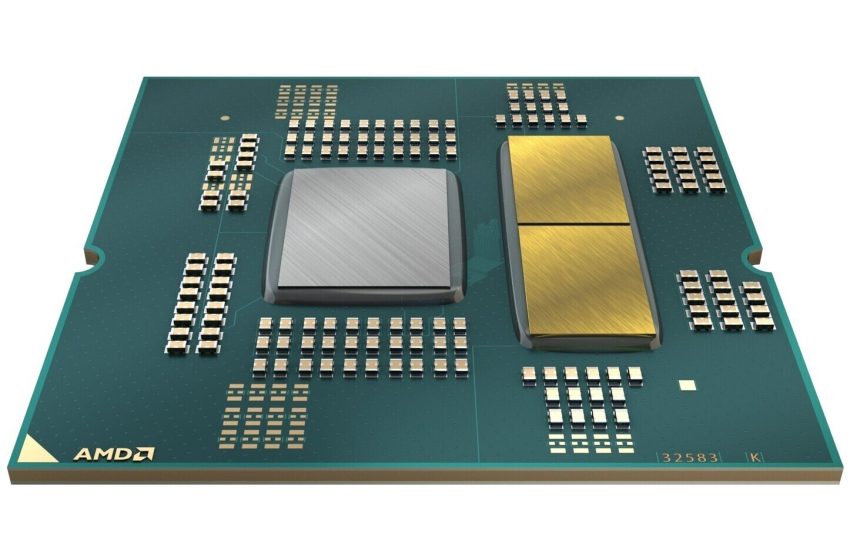

AMD Ryzen 10000 “Olympic Ridge” to Debut with 6/8/10/12/16/20/24-Core “Zen 6” SKUs

The upcoming Ryzen 10000 series is expected to land on AMD’s AM5 socket, extending the socket life for another processor generation and confirming AMD’s long-term socket selection. For other specific information, AMD plans to implement up to 4 MB of L3 cache per core for a total of 48 MB of L3 cache per CCD, and a total of 96 MB of L3 cache for the fully-fledged 24-core SKU. This is, of course, before adding any 3D V-Cache enhancements that AMD is known for when it comes to boosting gaming performance. AMD is able to pack this much punch because TSMC’s N2 2 nm technology packs more than 200 million transistors per mm², depending on the configuration and whether AMD chooses the high-density or high-performance variant.

AMD is enriching its “Zen 6” cores with 16-bit AVX-512 calculations that will now be possible on consumer-oriented desktop CPUs, allowing developers to efficiently accelerate applications and data paths that leverage AVX-512. It is bringing feature parity with Intel’s best x86 extensions, meaning that useful advanced vector extensions like AVX512_BMM, AVX_NE_CONVERT, AVX_IFMA, AVX_VNNI_INT8, and AVX512_FP16 are coming to consumers to accelerate software running locally, and not just for expensive Xeon CPUs that Intel usually reserved these extensions for.

First Appeared on

Source link